USB接口

USB接口

THEDIUSB介绍

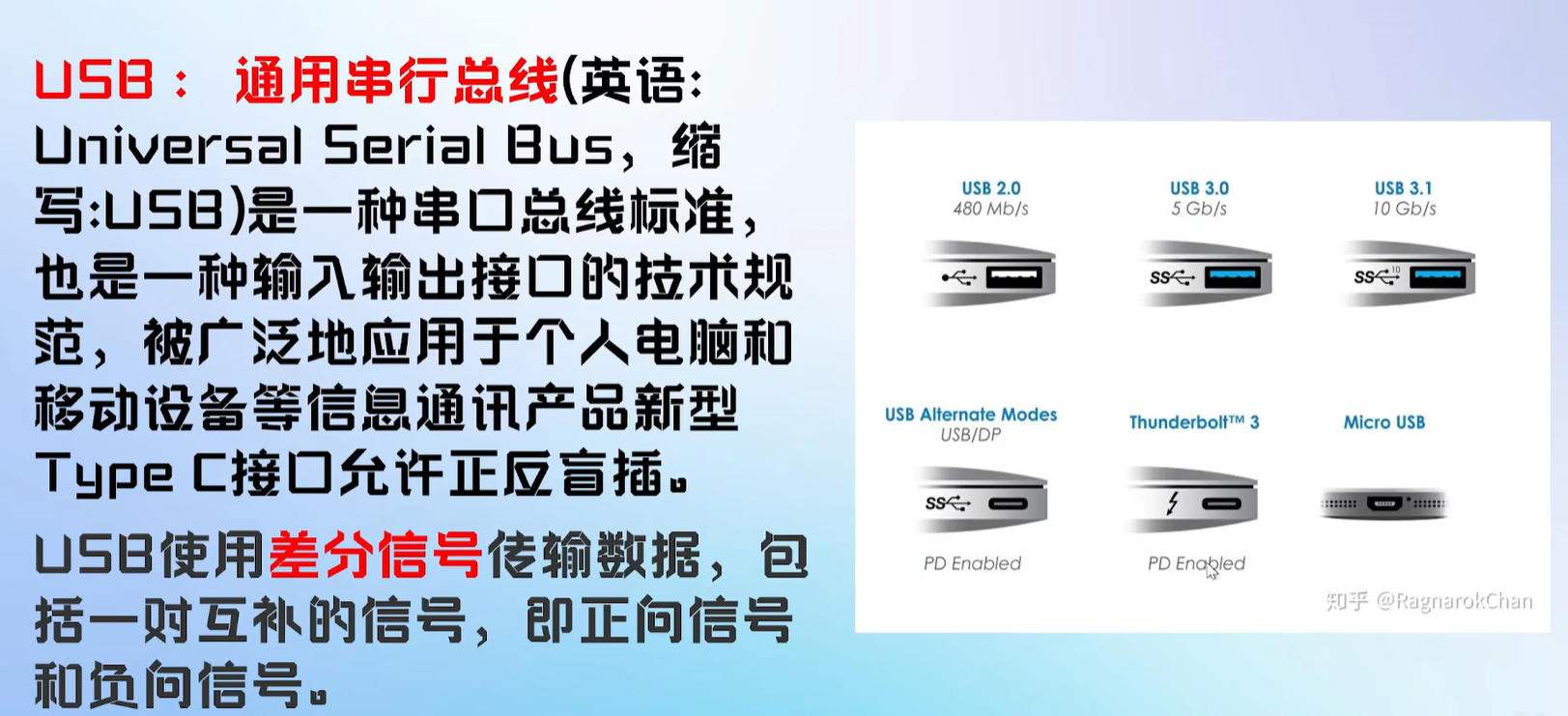

USB概念

单端信号与差分信号

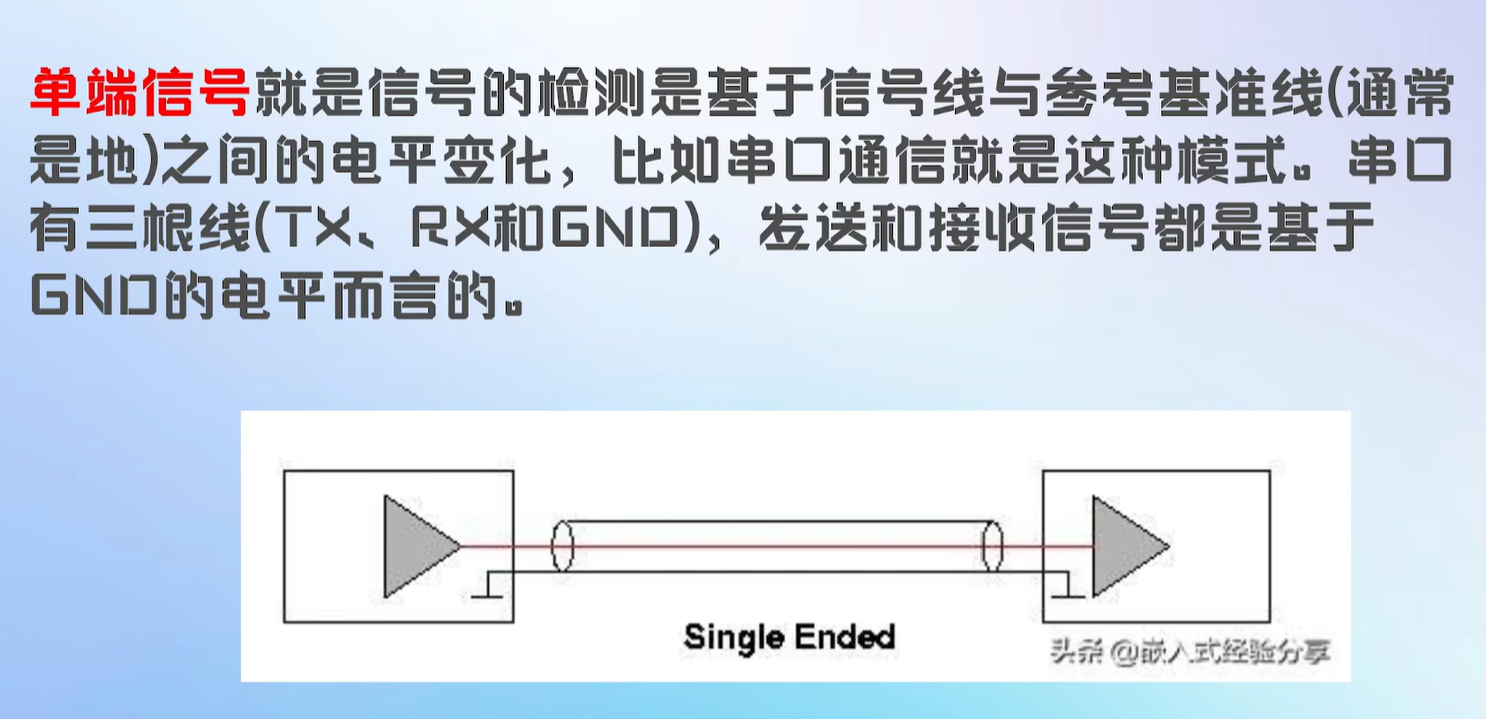

单端信号:

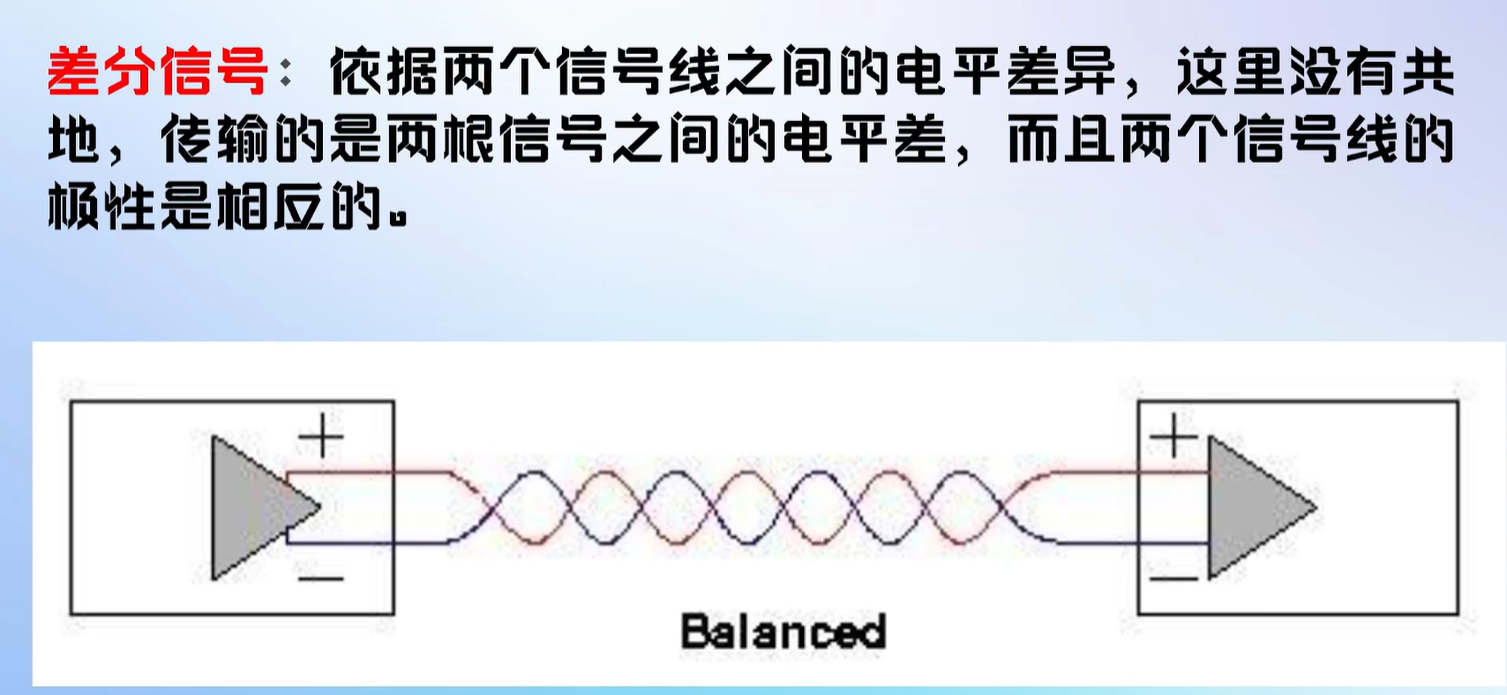

差分信号:

接收到的信号是两个信号线的电平差

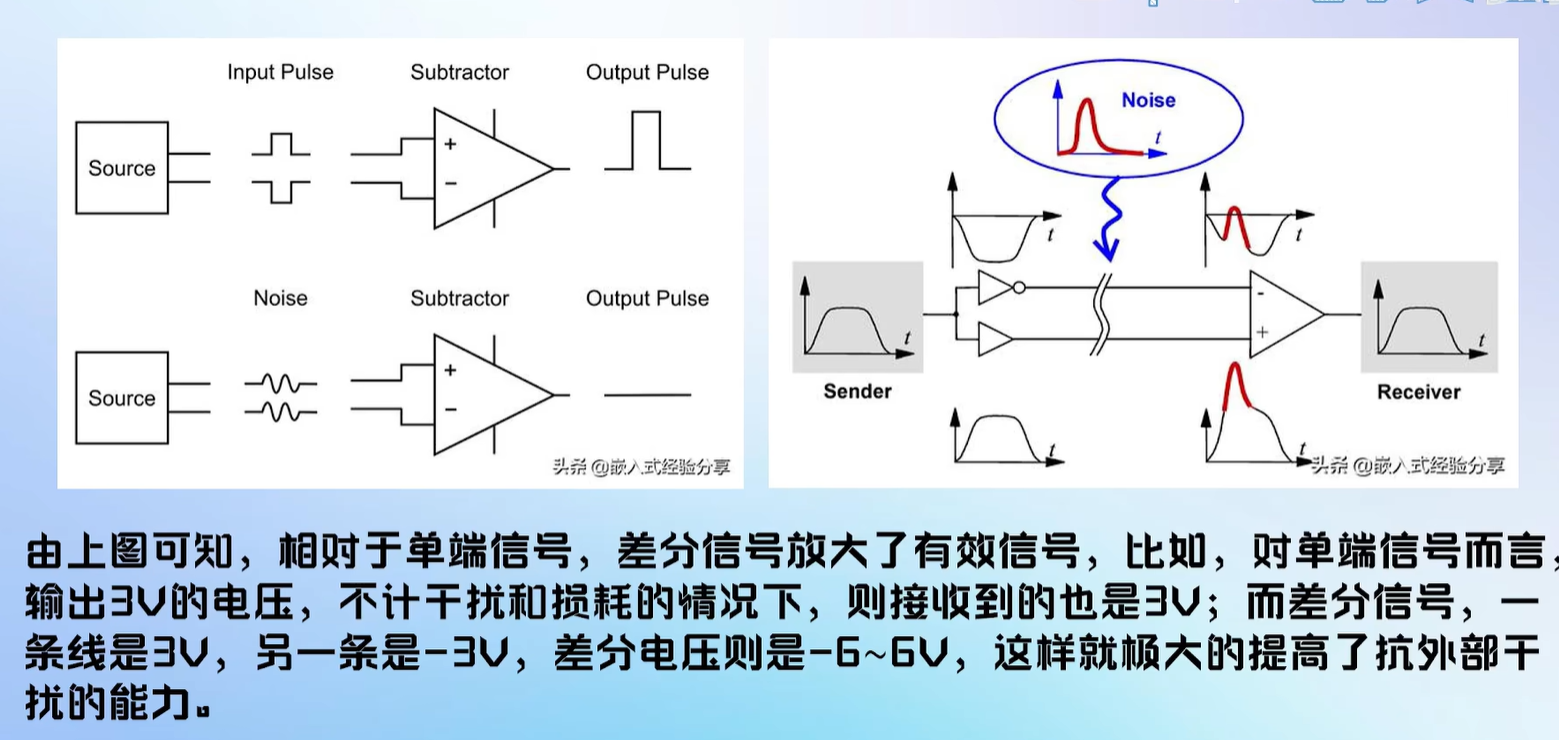

差分信号的好处

**差分信号的抗干扰能力强。**因为两根差分走线之间的耦合很好,当外界存在噪声干扰时,几乎是同时被耦合到两条线上(两信号电压都变化,但是差值还是不变),而接收端只是关心两信号的差值,所以外界的共模噪声可以被完全抵消。

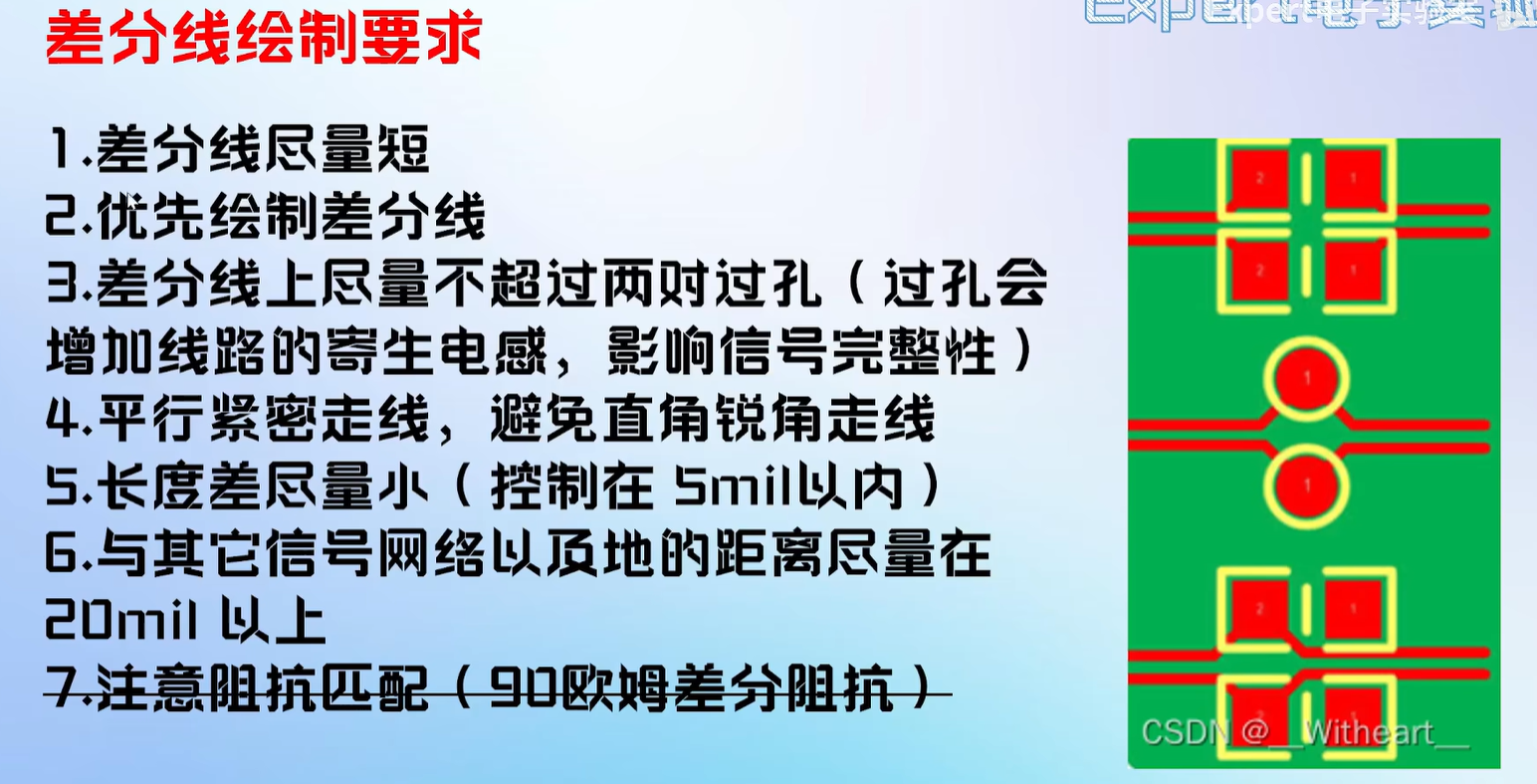

PCB设计差分线绘制

优先绘制差分线

差分线尽量短,避免受到一些干扰及信号的衰减

差分线上不要超过两对过孔

平行紧密走线,避免直角锐角走线

长度差尽量小(控制在5mil以内),尽量保证差分线等长!!!

与其他信号网络以及地的距离尽量在20mil以上(避免和其他信号发生相互干扰)

注意阻抗匹配(90欧姆差分阻抗)

对于阻抗匹配问题,对于高速信号非常的重要,是PCB设计中非常重要的一环,可以使用嘉立创阻抗设计神器进行阻抗设计

USB接口

TYPE-A

USB Type-A又可称为USB-A

TYPE-B

TYPE-C

USB TypeC 拥有诸多优点:双面可插不担心正反、可做USB/雷电高速传输载体,支持 PD快充、音频设备、HDMI传输、调试模式等诸多功能。

市面上的其他USB接口和充电接口在逐步被TypeC替代,可以预见的是,TypeC作为一种多兼容性接口,其未来会具有非常长的生命周期。

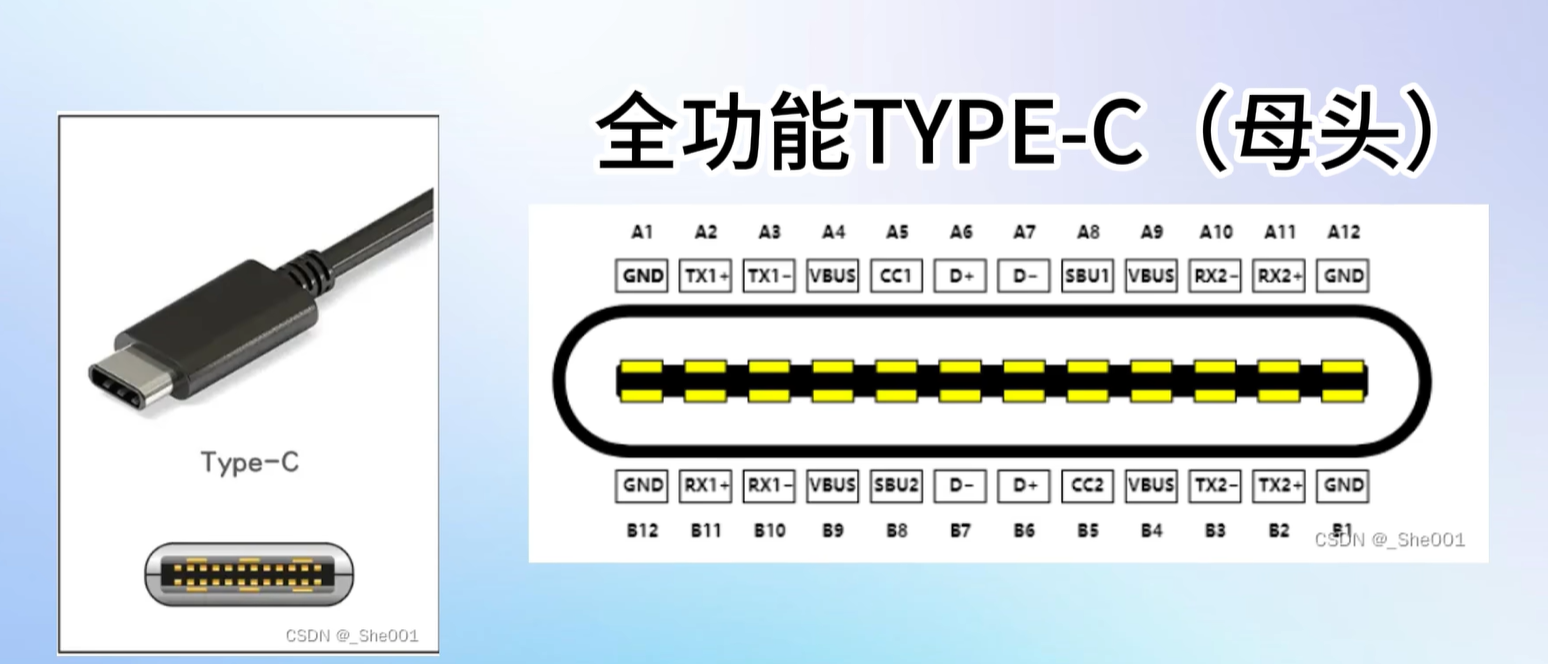

主要就是这几种: 24Pin、16Pin、6Pin USB-TypeC接口的引脚,以及USB-PD、USB接口类型。

**6Pin:**用于只需要USB取电充电,无法传输数据

**16(12)Pin:**用于只有USB2.0协议的情况

24Pin(完整版):使用USB3.0协议

A2 A3 A10 A11 B11 B10 B3 B2这八个引脚用于USB3.0传输

A6 A7 B7 B6 USB2.0传输

B8 B9 备用引脚一般不适用

A5 B5 这两个是CC引脚,用于快充

一文读懂USB TypeC与USB-PD。TypeC引脚定义-24P 16P 6P,CC1、CC2的作用,USB-PD介绍,USB2.0/3.0接口类型一览-CSDN博客

CC引脚

一文详解Type C-CC引脚的作用_typeccc1cc2作用-CSDN博客

在 USB Type-C 接口中,CC1 和 CC2 引脚的上拉和下拉电阻的配置非常重要,因为它们直接影响到设备角色的判定和电源协商。它们的作用主要是通过电阻的拉高(上拉)和拉低(下拉)来识别设备的角色(源或接收端)以及连接方向。

上拉电阻(通常使用5.1KΩ,连接到 VBUS):标识设备为 源设备(充电器、供电端)。

下拉电阻(通常使用5.1KΩ,连接到地):标识设备为 接收设备(接收电源的设备,如手机、笔记本等)。

不同使用的接线方法:

只需要取电(从公头取电):CC1和CC2分别下拉一个5.1KΩ的电阻到地即可

使用PD快充:CC1和CC2分别上拉一个5.1KΩ的电阻到VBUS即可

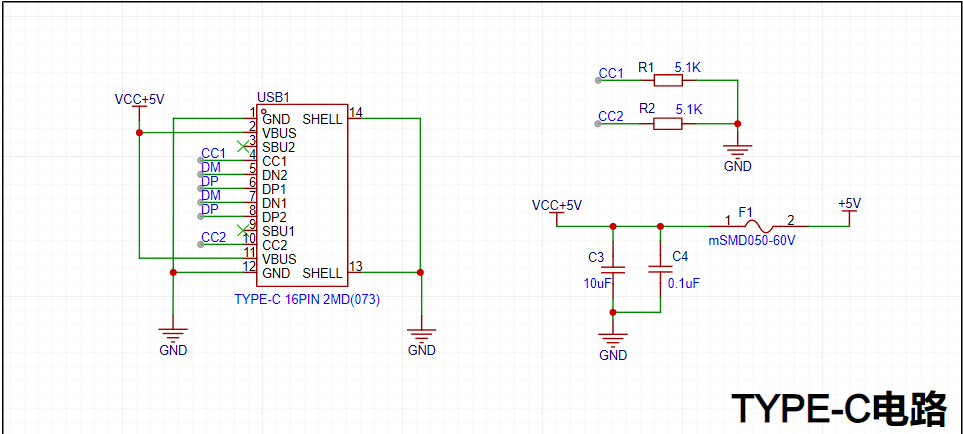

以下是我在设计电路时使用到的接口

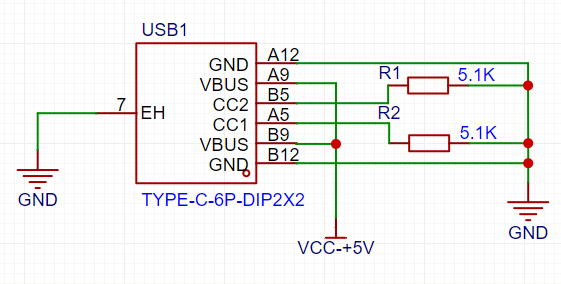

TYPE-C-6Pin

这里的VCC是输入的电源5V,GND就是地

EH引脚:就是一个固定的针脚,直接接地的话可以让其更加牢固

**CC1和CC2作用:**识别设备,分别接5.1K欧电阻下拉。悬空的话VBUS就没有电源输入

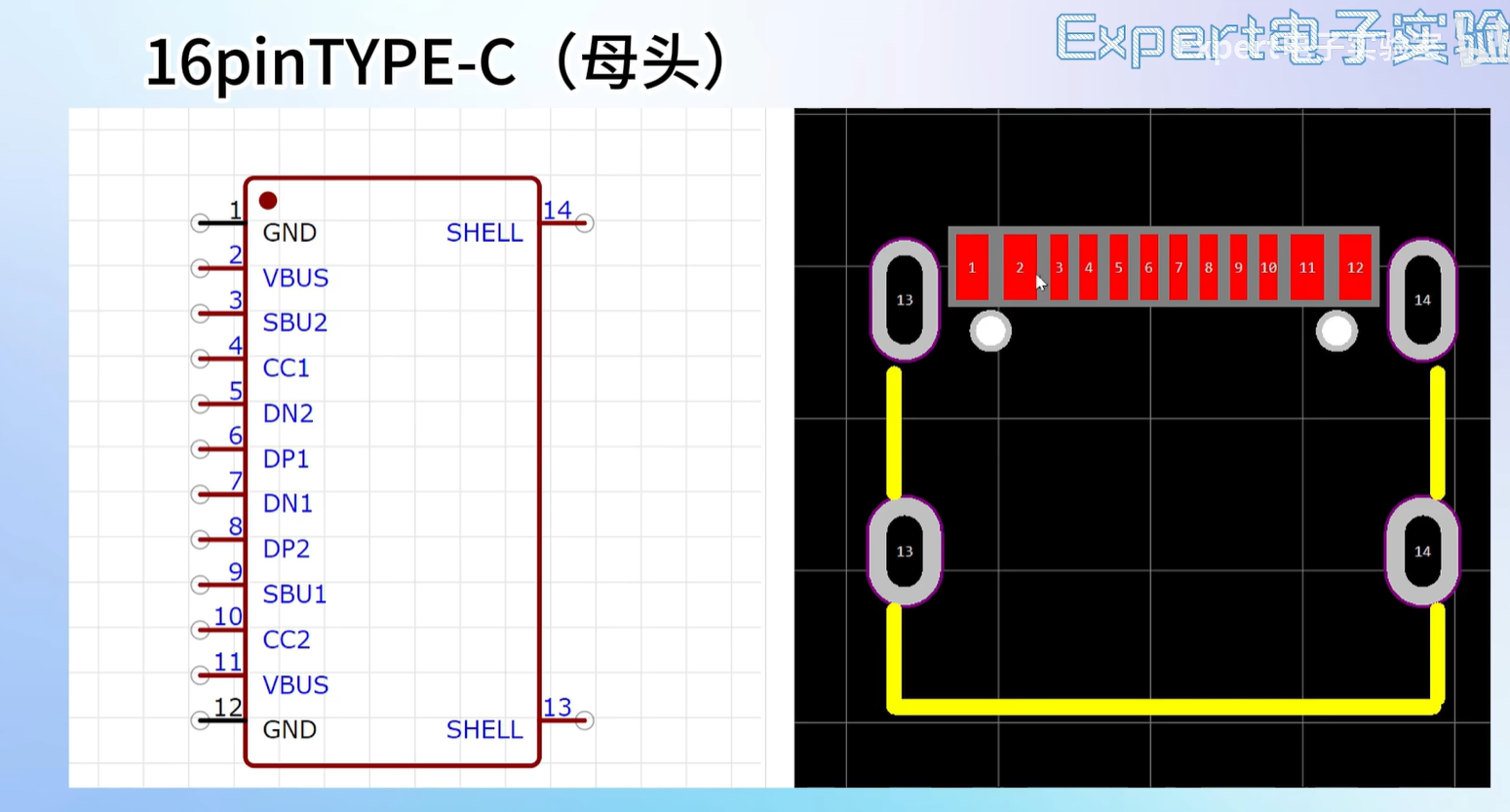

TYPE-C-16Pin(12Pin)

16Pin一般为接口厂家、封装的正式名称,而日常生活中习惯称呼为12Pin。这是因为接口设计时,将TypeC母座同侧两端的两个Vbus及GND出线都并拢了起来,虽然从口那里看是16条出线,但座子后面的焊盘只有12个(VBUS合并了、GND也合并了)。

DP和DM是数据线,分别是差分信号的+和-,有两个DP和DM分别是因为对称设计支持正反插的功能,分别取相同的网络标签即可

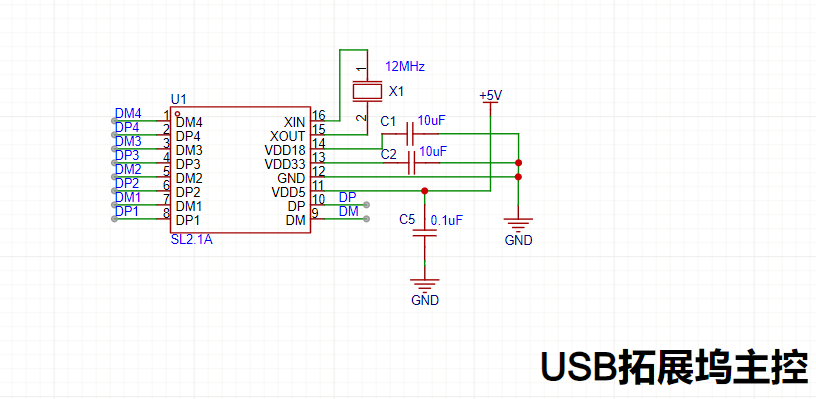

这里的DM和DP接到了SL2.1A上做输入信号

SBU1和SBU2是扩展功能使用,这里选择不连接符号

USB转串口(TTL)芯片

在设计完最小系统板之后,我们的电路板仅仅能满足芯片跑起来的基本功能,如果要调试芯片,则需要购买USB转TTL模块、杜邦线,也要把IO0和EN引脚焊接出来,使用并不方便,有哪些可以优化的地方呢?

1、添加USB线供电、烧录、调试电路

2、添加自动下载电路

此时就需要我们的CH340芯片和添加自动下载电路

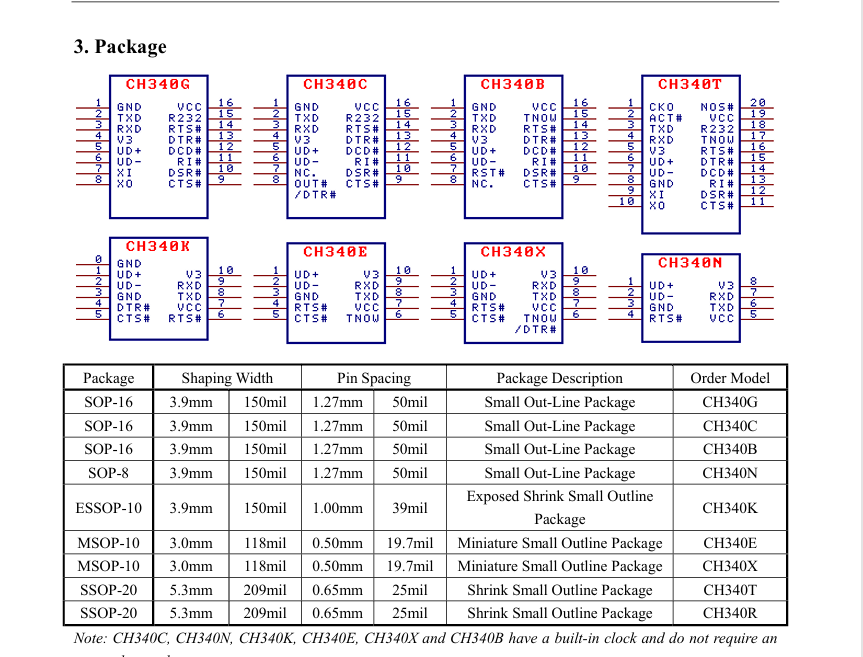

CH340系列

我们在CH340的数据手册中,发现该芯片有很多类型,具体差别可以在手册中找到

具体差别介绍:USB转串口芯片CH340的使用_ch340c-CSDN博客

我们常用的是CH340C,这个芯片CTS和DSR引脚,可以用于自动下载电路的设计

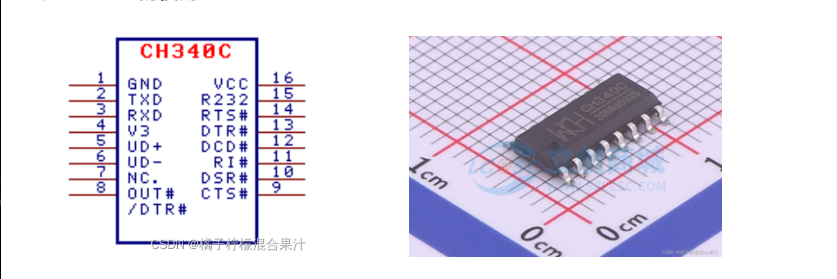

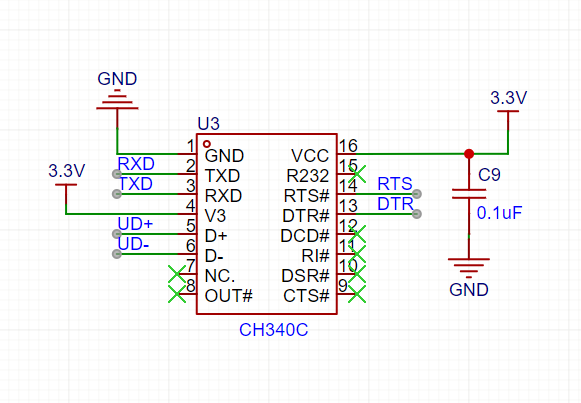

CH340C

引脚定义:

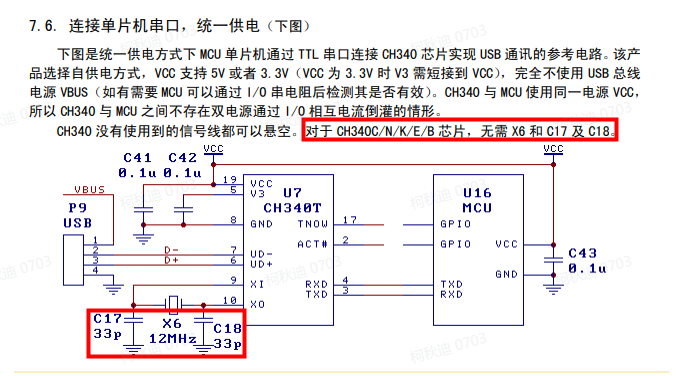

- **数据手册7.6:**连接至MCU串口,统一供电示例电路

实际原理图绘制:

根据手册中的描述:我这里是3.3V供电

V3引脚:连接3.3V输入电源如果是5V供电,将这里改成一个0.1uF的电容接地即可

VCC引脚:连接3.3V输入电源,接一颗0.1uF去耦电容

D+和D-引脚:连接至USB的D+和D-信号

RXD和TXD:TXD引脚连接至MCU的RXD,RXD连接至MCU的TXD

RTS和DTR:与自动下载电路有关,连接至单片机下载电路相关引脚,见下方

串口自动下载电路

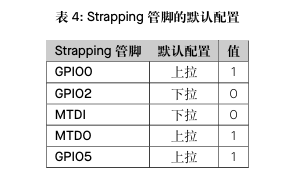

以ESP32为例,手册上描述:

在复位上升沿时,GPIO0为1,则进入FLASH运行模式,此时内部程序正常运行。

在复位上升沿时,GPIO0为0,则进入BOOT模式,此时可通过串口下载程序。

**手册上GPIO0和GPIO2的默认配置为:**GPIO0默认上拉(高),GPIO2默认下拉(地)

EN引脚:也是默认高电平

总结:GPIO0和EN引脚默认为高电平

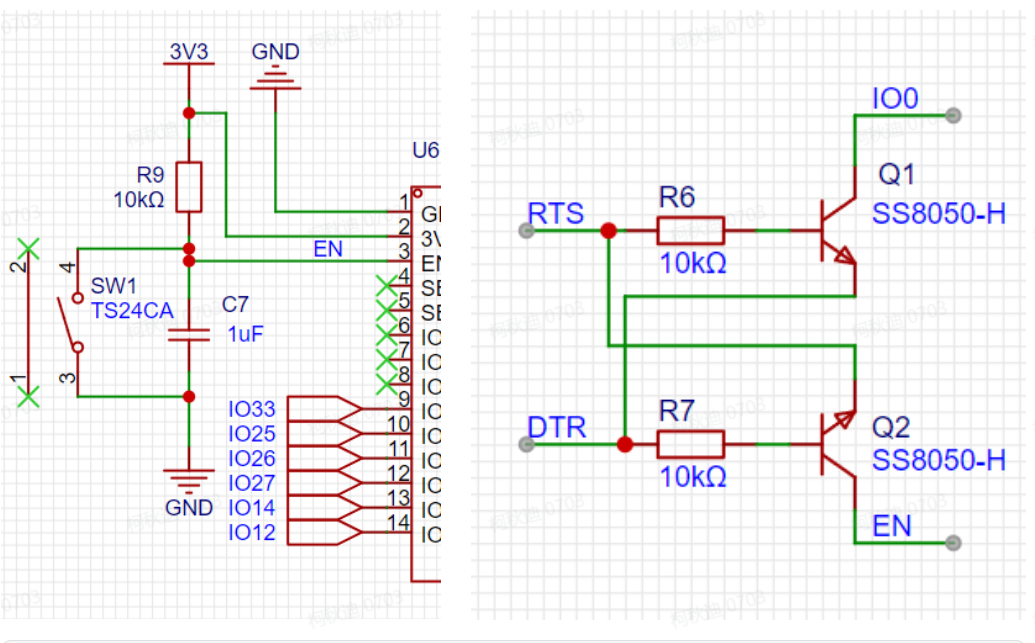

自动下载电路实现:

所以ESP32要进入下载模式的前提是,IO0拉低,然后复位芯片(通过EN引脚控制,EN由低电平到高电平(上升沿)时CPU复位,复位后检测到GPIO0是低电平,MCU自动进入下载启动模式!)

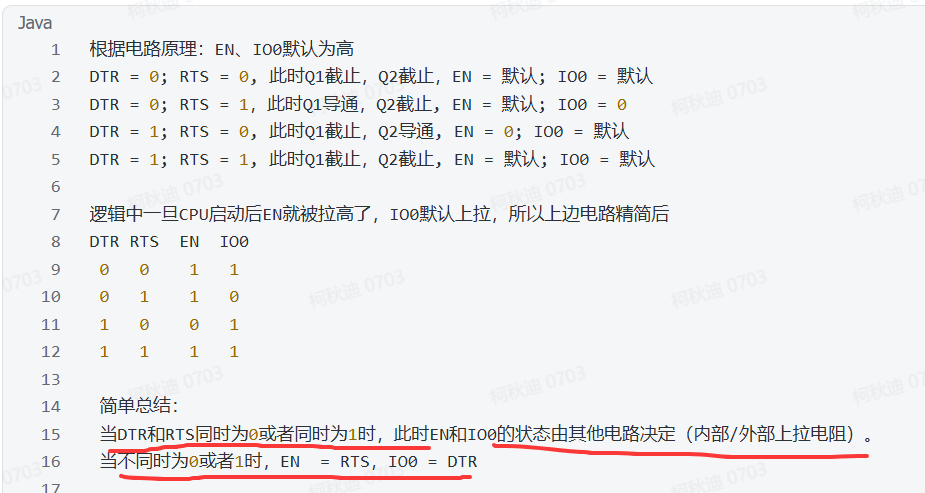

逻辑表如下:

总结:

当DTR和RTS同时为0或者同时为1时,此时EN和IO0的状态由其他电路决定(内部/外部上拉电阻)。

当不同时为0或者1时,EN = RTS,IO0 = DTR

但是这种逻辑下 EN和IO0是不可能同时为0的,然而进入下载模式则需要如下的序列

IO = 0,EN = 0

IO = 0,EN 0 -> 1

从逻辑表上看是根本无法正常进入下载模式的。

问题的答案实际在另外一部分电路,原理其实非常简单: EN信号连接在一个

电容充放电电路上(上方的左图),在上电的瞬间,EN由于电容充电,电平并不会立马变为高电平,而是缓慢上升,我们就可以使用这个时间差。1、设置DTR = 1; RTS = 0, 此时 EN=0,IO=1

2、设置DTR = 0;RTS = 1,EN=0,IO=0 此时EN引脚由于电容充电,实际还是0

3、等待电容充电完成,此时 EN=1 ,IO=0,芯片进入下载模式

即实现自动下载电路

具体的DTR、RTS的时序控制是由芯片厂家提供的esptool.py下载脚本进行设置以实现上方下载模式所需要序列!!!

如何使用脚本:

我们虽然可以使用脚本实现序列

但是我们一般使用IDE进行开发,比如:Clion+platformio,或Vscode+platformio,因为PlatformIO 内部集成了 esptool.py脚本,烧录时自动管理 DTR/RTS,所以我们直接在IDE内部点击下载即可

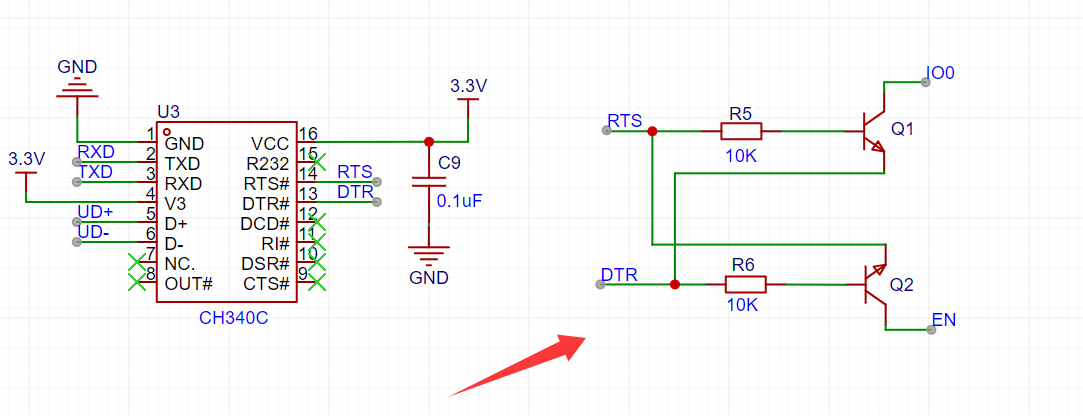

自动下载电路原理图:

左边是CH340芯片,相关引脚为RTS和DTR,右边是自动下载电路的电路

三极管左边的电阻:在基极起限流电阻作用,通常用10K即可,太小可能会烧坏三极管